JTAGulator

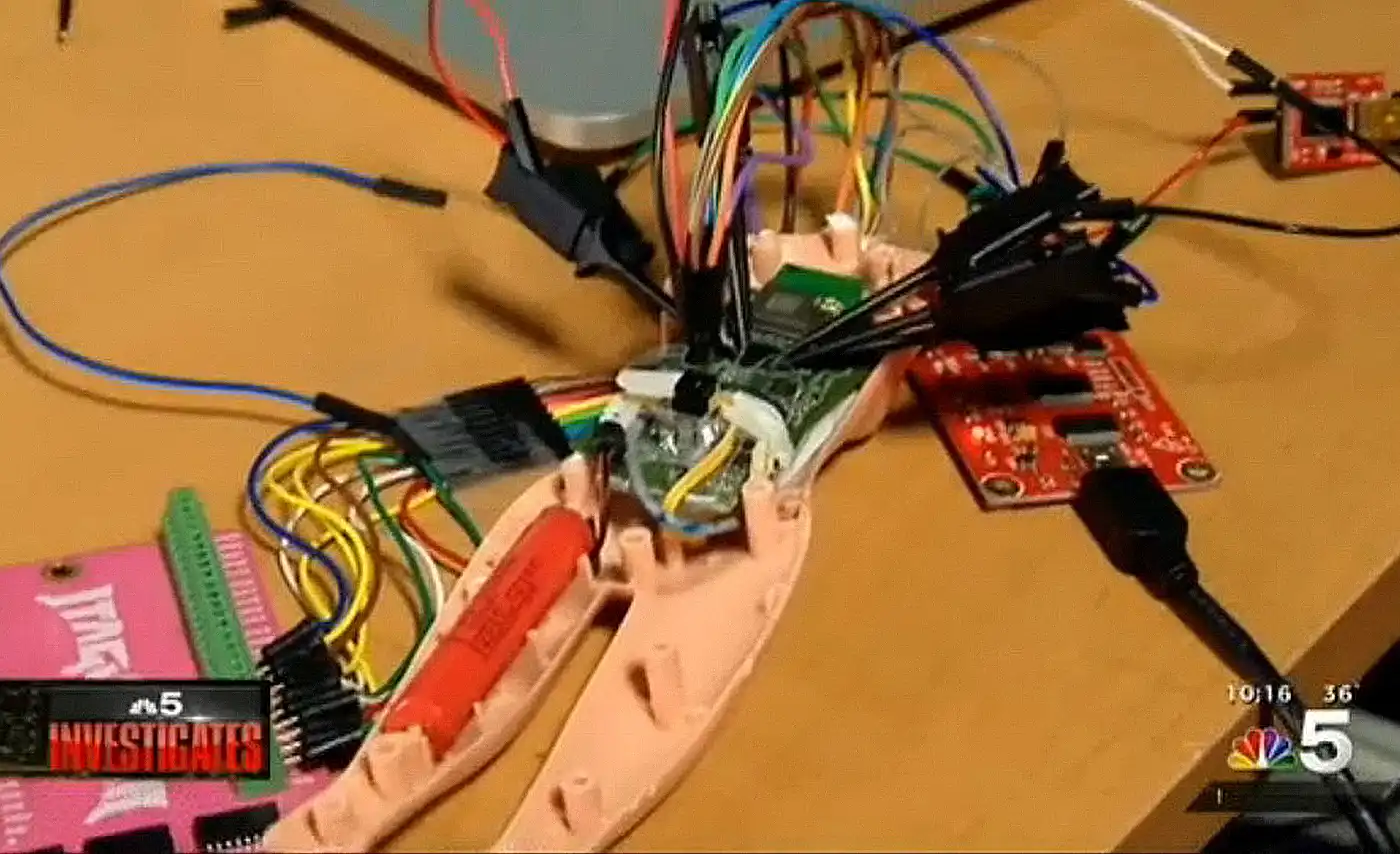

On-chip debug (OCD) interfaces can provide chip-level control of a target device and are a primary vector used by engineers, researchers, and hackers to extract program code or data, modify memory contents, or affect device operation on-the-fly. Depending on the complexity of the target device, manually locating available OCD interfaces can be a difficult and time consuming task, sometimes requiring physical destruction or modification of the device.

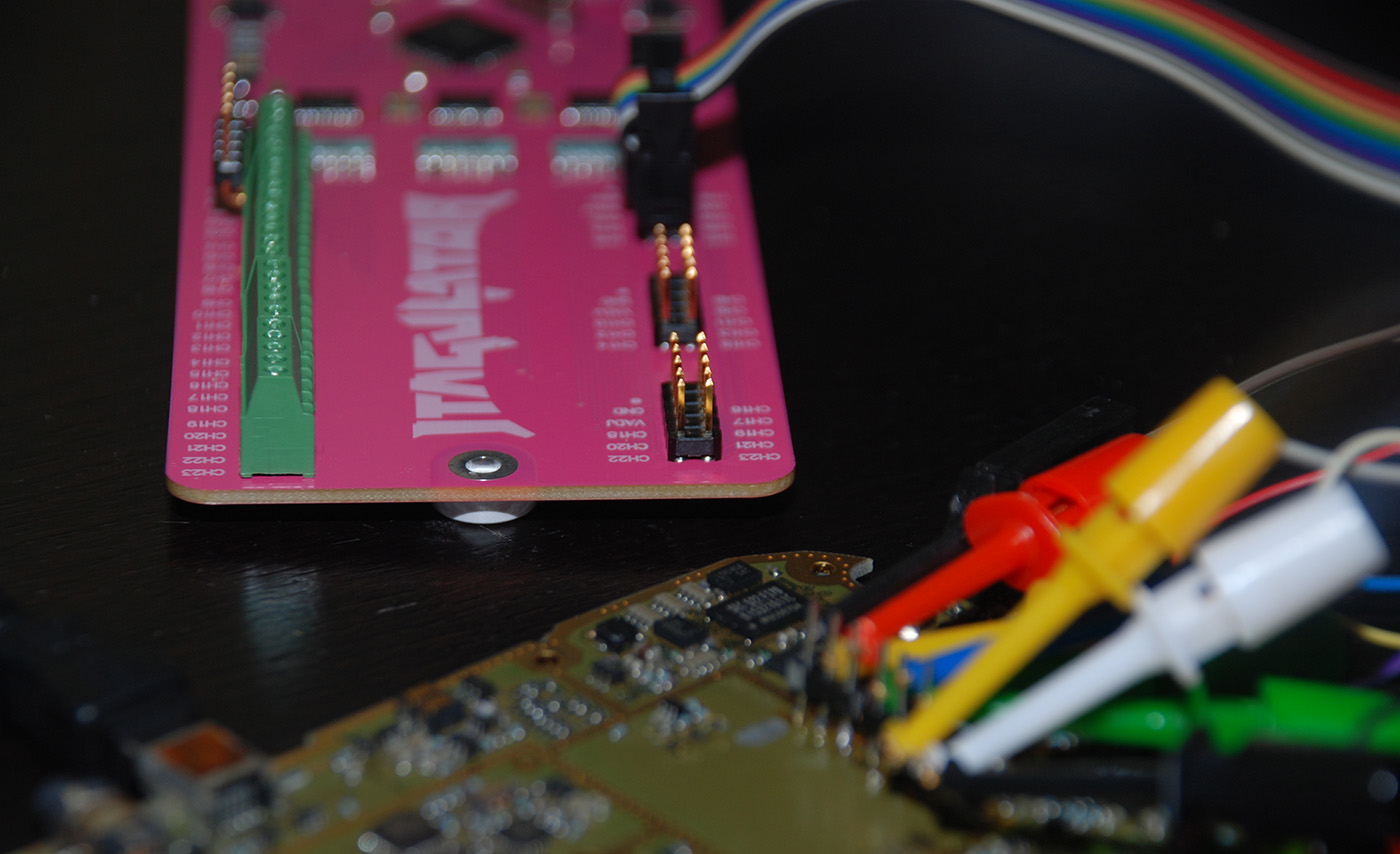

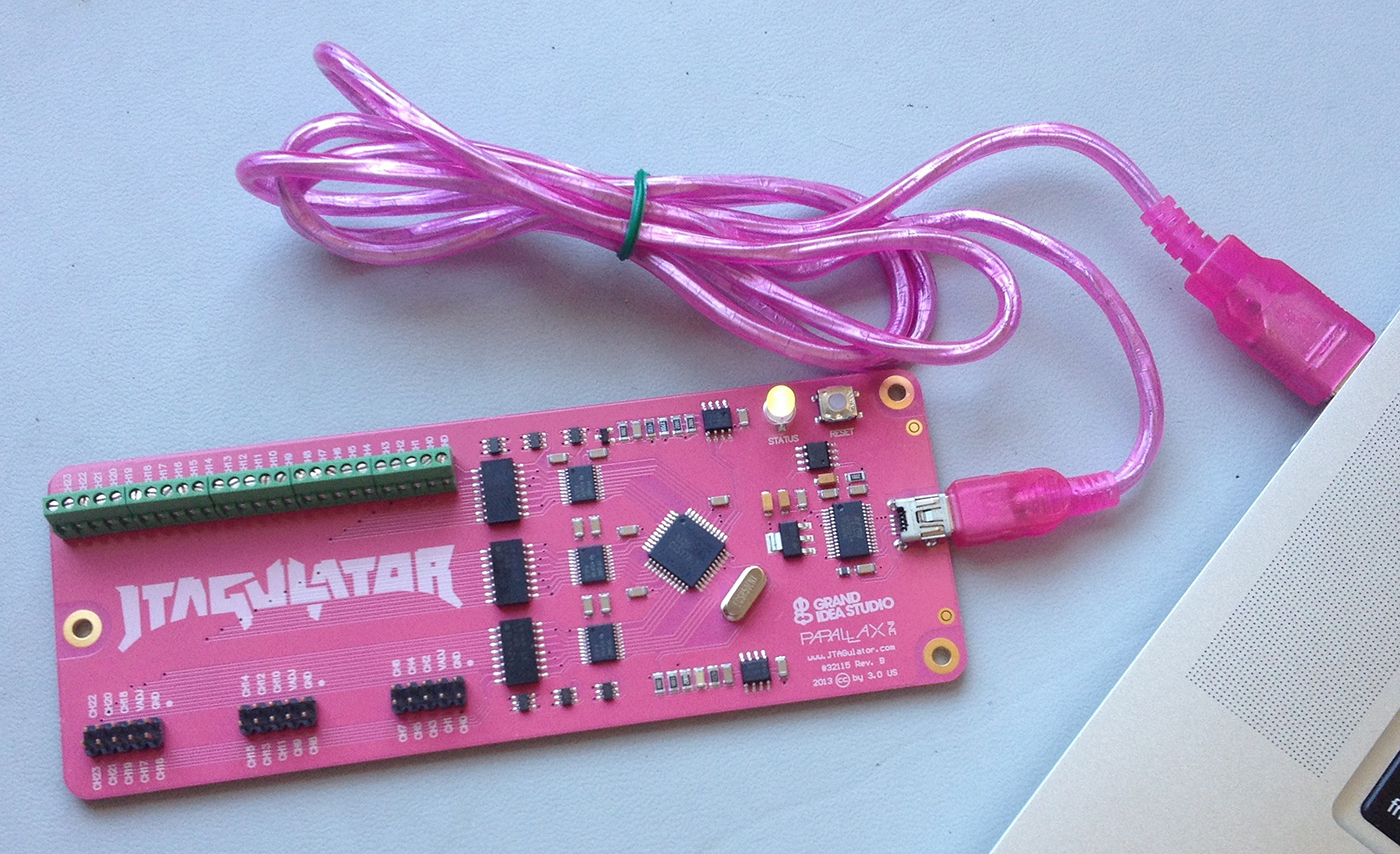

JTAGulator is an open source hardware tool that assists in identifying OCD interfaces from test points, vias, component pads, or connectors on a target device.

From 2013 to 2023, Parallax, Inc. was the official hardware manufacturer of the JTAGulator. As of July 2025, EXPLIoT is the official hardware manufacturer and maintainer. For support, visit their project page or Discord server. To purchase a JTAGulator, visit their store.

This design is distributed under a Creative Commons Attribution-ShareAlike 4.0 International license. The JTAGulator name and logo are registered trademarks of Grand Idea Studio, Inc. The trademarks may not be used on derived works without permission.

Features:

Documentation:

- Wiki (GitHub)

- Frequently Asked Questions (GitHub)

- Block Diagram

- Schematic

- Bill-of-Materials

- Assembly Drawing

- PCB: Gerber Plots, Altium Designer, and OSH Park

- Test Procedure and Video (YouTube)

- Source Code: Parallax Propeller (GitHub)

- Development Tool: Parallax Propeller Tool for Windows (v1.3.2)

Additional Resources:

- Video: New Feature Update (YouTube)

- Video: Introduction and Demonstration (Expanded) (YouTube)

- Video: Updating Firmware (YouTube)

- Video: Pin Mapper (EXTEST Scan) (YouTube)

- Video: Black Hat Asia 2014: JTAGulator Part 1 and Part 2 (YouTube)

- Slides: JTAGulator: Assisted discovery of on-chip debug interfaces (Revised September 16, 2018)

- Poem by Zach Houston

Raspberry Pi Zero W:

Environment to demonstrate JTAG, UART, and logic analyzer functionality.

- Notes

- Sample Code (Python 2.7.17)

- OpenOCD Configuration

Acrylic Case:

- Bill-of-Materials

- Bill-of-Materials (w/ Sparkle Add-On Board)

- Design Files

- Assembly Video (YouTube)

Sparkle Add-On Board:

Provides neon pink underglow for maximum aesthetics. Connects to the JTAGulator with pogo pins. LEDs will turn on when the target voltage (VADJ) is set.

- Schematic

- Bill-of-Materials

- Assembly Drawing

- PCB: Gerber Plots and OSH Park

- Pictures (Flickr)